ALU on #Tangmega138k isn't working, but for some reason I have a good feeling about today.😀 #fpga#apicula

#Tangmega138k

So, I made 8 FlipFlops and placed them in each of the 8 quadrants of #Tangmega138k #fpga. Each DFF is connected to its own LED and transmits the button status to it.

#nextpnr successfully routed through the central bridge to all 8 quadrants.

gowin_pack wrote all the fuses and, in addition, 9 special ones for clock enabling in the quadrants and bridge.

@WillFlux Um... not so fast :)

I will bring #Tangmega138k support in #apicula to a state where some #riscv will run, but then I will need to go back to GW5A-25A and focus on DSP and serial IO.

At this point, there won't be a PLL support to run #isle. I hope someone will join in and implement PLL :)

But in any case, #isle will be launched on 138 this year, as I promised.😉

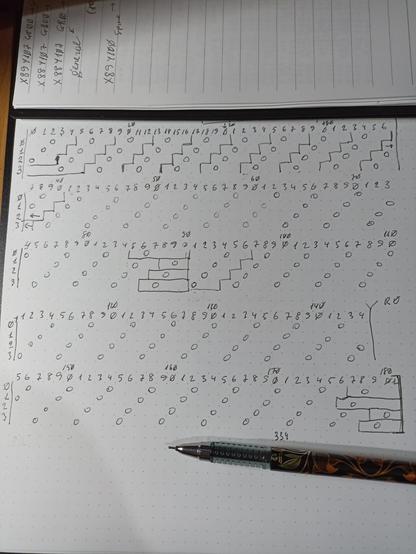

After 100500 checks which spine connects to which cell, the picture with the clock in #Tangmega138k becomes a little clearer🤣 #fpga

Gee!

First attempt to compile a design from a button, flip-flop and LED on #Tangmega138k. Clock wire routing failed. 🤣

We'll look into what the problem is.

#fpga#apicula#sipeed#gowin

So, it's a new year and we're getting started with the terrifying and magnificent clocks of #Tangmega138k

The situation is somewhat complicated by the fact that, for some reason, the external generator is connected to a standard IO rather than one dedicated to the clock.

(Yes, it says EMCCLK, but for #fpga it's just IO.)

In other words, I won't be able to easily send the clock signal directly to the spine, but will have to implement a gate ‘normal wires’ -> ‘clock wires’.😜