NXP tl T6C10V0C. Anyone know what that is? Mask date of 2012. #ICRE #ICReverseEngineering

#ICRE

Slightly disappointed. Decapped the Rucify ASIC from a Zip drive last night. Can't see anything through the brown polyimide topcoat. Flame torching the topcoat didn't do anything, but a hot rosin boil removed the die attach compound.

This is going to need some headscratching. #ICReverseEngineering #ICRE

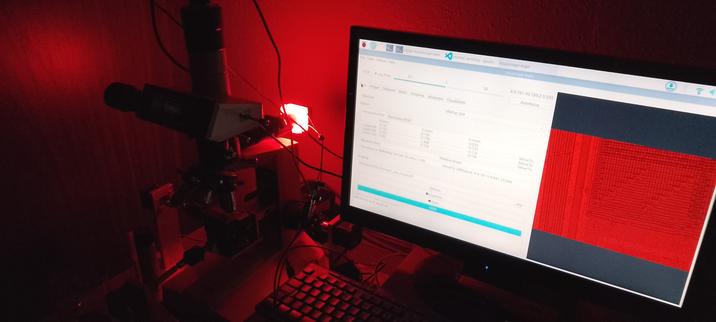

We regret to inform you that the #ICRE rig has been possessed.

Another great #38c3 talk, "Proprietary ICs and dubious marketing claims - let's fight these with a microscope!" by Giulio Zausa.

Reverse engineering the gate arrays from a Roland piano using Inkscape and Verilog - neat!

Great talk by Aedan Cullen (@aedancullen) at #38c3 on breaking security on the #RP2350 by glitching the OTP VDD.

https://streaming.media.ccc.de/38c3/relive/625

I expect the bus between the state machine and OTP is like Wishbone or M68K and has a request and an acknowledge, and the data is latched on the ACK. No ACK? Guard word stays in the latch.

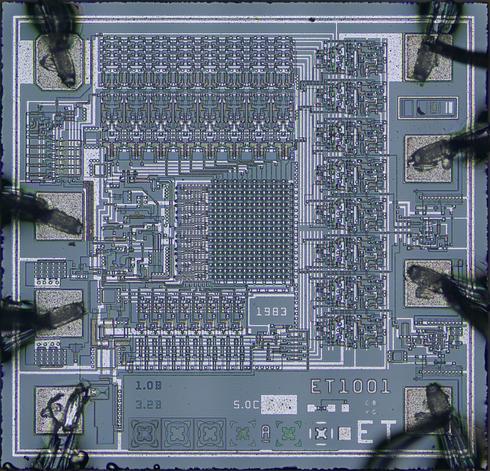

It's the Freya's day today so let's run another #nakeddiefriday why don't we.

Today I got a #French classic form 1983, one of the very first chip cards. The micromodule is a very characteristic shape of those designed by Bull.

On the die itself, the EEPROM array is in the very center, with the address counter to the right, drivers above and the data multiplexer below.

Note the designer initials, C.B. and Y.G.

Hi-res: https://siliconpr0n.org/archive/doku.php?id=infosecdj:bull:et1001

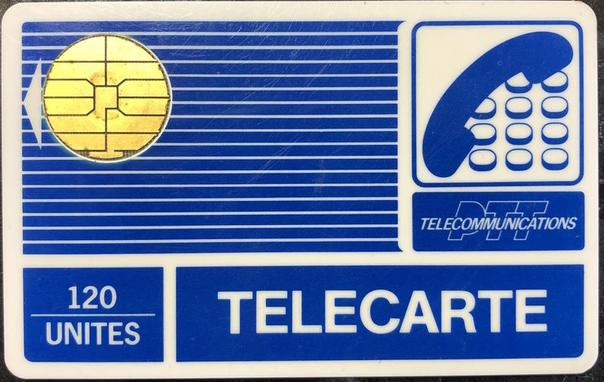

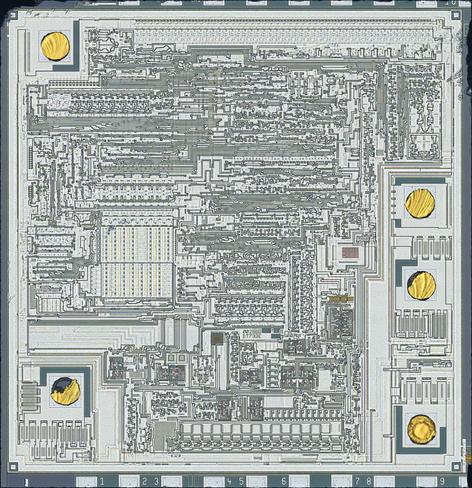

It's been a while since last #nakeddiefriday so here we go.

Today's exhibit comes from a German payphone card (remember them?). Infineon M2332-B1. What is interesting, is the decision to fill as much top metal as possible, making the die look very much like hobby-made milled PCBs.

More: https://siliconpr0n.org/archive/doku.php?id=infosecdj:infineon:m2332-b1

N.B. If you look closely, you will find a sun. 🌞

the grind goes on.

https://dev-zzo.github.io/blarg/2024/07/31/siemens-m1327a3-part-7.html

a short one, where I look at the clock input circuit.

the RE train has moved a but further.

https://dev-zzo.github.io/blarg/2024/07/30/siemens-m1327-part-6.html

I get to look at the counter 3 today.

new blog post!

https://dev-zzo.github.io/blarg/2024/07/28/deprocessing-attempt-3.html

in which I explore deprocessing a bit further on my 3rd attempt.

here he goes again with this stuff

https://dev-zzo.github.io/blarg/2024/07/27/siemens-m1327-part-5.html

this time it's another counter, a simpler one.

wouldn't you know it.

https://dev-zzo.github.io/blarg/2024/07/25/siemens-m1327-part-4.html

in this part I take a look at a 6-stage counter and its supporting circuitry.

worked all night (no) to bring you the next installment of the blarg.

https://dev-zzo.github.io/blarg/2024/07/23/siemens-m1327-part-2.html

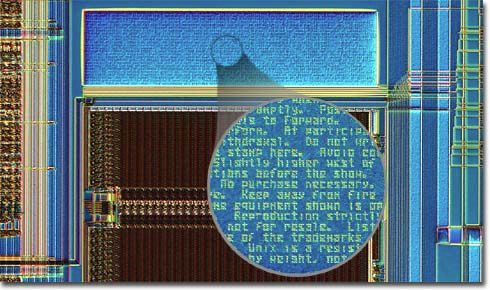

Of all the chips I'd like to find and stick under the microscope, the Hewlett-Packard ASPEN (Acquisition Signal Processing Engine) from the 54600 series oscilloscope is near the top of the list.

Why? Just to image this disclaimer.

photo: https://micro.magnet.fsu.edu/creatures/pages/disclaimer.html (C) M. W. Davidson and FSU

Oh, it's #nakeddiefriday today. I got an interesting specimen, a very old and dead GSM SIM card with an ST chip in it.

You can see EEPROM, mask ROM, RAM, and the CPU core very clearly. I wonder if the mask ROM can be read.

More: https://siliconpr0n.org/archive/doku.php?id=infosecdj:st:st16f48a

If you remember the ARM250 I decapped earlier ... I've uploaded a zoomable 100x photo to Silicon Pr0n: https://siliconpr0n.org/map/gec-plessey/arm250/philpem_mz_ms10x/

Tech info: https://siliconpr0n.org/archive/doku.php?id=philpem:gec-plessey:arm250

original thread: https://digipres.club/@philpem/112620630504333892

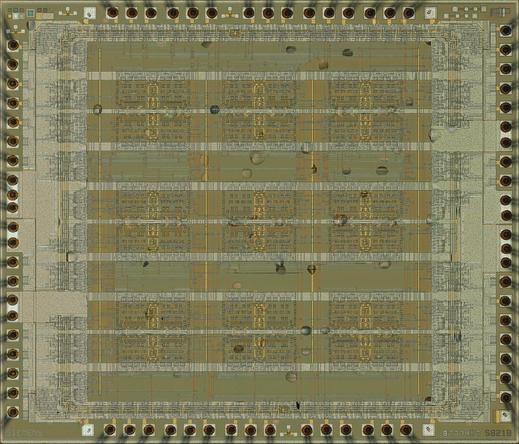

Hey y'all. Today's the #nakeddiefriday, it's rainy af, and what I have for you today is a Siemens ASIC I know nothing about.

This comes from a batch of similar packages in PGA labelled SH100 or SH100CK. The array is a 3x3 matrix of cell blocks made with bipolar tech, each block having components for 8 gates with some shared (bias?) circuitry.

More and hi-res at: https://siliconpr0n.org/archive/doku.php?id=infosecdj:siemens:sh100ck-b1114b1

I'm hitting a fun problem with the ARM250TG #ICRE. There's a 41x47 array of tiles, each tile is 4056x3040 pixels. Overlap should be about 20%.

That means a final image of 133037 by 114304 pixels, give or take.

In unrelated news, I'm debating whether to buy 128GB of RAM and an RTX GPU for my desktop machine...