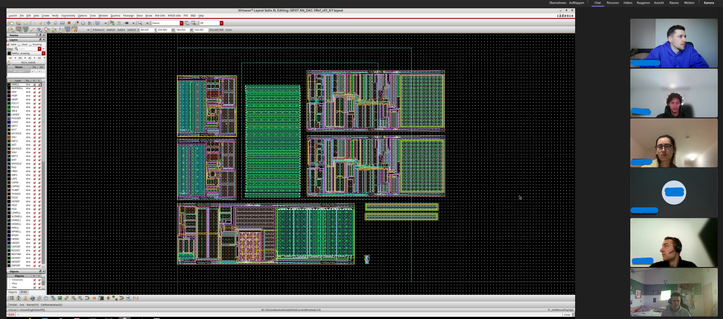

MediaTek’s First 2nm Chip To Tape-Out In September 2025 #2nm #chip #computex2025 #dimensity #mediatek #mobile #mobilephones #production #ricktsai #semiconductorchips #silicon #tapeout

https://www.lowyat.net/2025/352259/mediateks-first-2nm-chip-to-tape-out-in-september-2025/