#computerarchitecture

even the diagramming isn't spared some psychedelic design

#computerarchitecture

ETH-Zurich: Digital Design and Computer Architecture; 227-0003-10L, Spring, 2025

https://safari.ethz.ch/ddca/spring2025/doku.php?id=start

#HackerNews #ETHZurich #DigitalDesign #ComputerArchitecture #Spring2025 #Education

Unusual circuits in the Intel 386's standard cell logic

https://www.righto.com/2025/11/unusual-386-standard-cell-circuits.html

#HackerNews #UnusualCircuits #Intel386 #StandardCellLogic #ComputerArchitecture #TechHistory

IBM press photo for a six-level copper interconnect in a 0.12µm process (1997)

František Kupka Two Grays II (1928)

#computerarchitecture #retrocomputing

Computer Engineering by S. A. Lebedev (Ed.)

This publication is concerned with a series of questions in computer engineering: the power supply system of the high-speed electronic computer of the Academy of Sciences of the U.S.S.R.; new elements and units for computers; a method of control of the arithmetic unit; a method of selecting the required word from the dictionary in machine translation; and present-day computer terminology. The publication was drawn up by specialists in the design and working of electronic computers. Besides papers from the Institute of Precision Mechanics and Computer Engineering, this publication contains articles by authors from other organizations concerned with computer engineering.

Translated From the Russian by JANE STUART

Translation edited by J.P. CLEAVE and E.A. SOWAN

You can get the book here and here.

Twitter: @MirTitles

Mastodon: @mirtitles@mastodon.world

Mastodon: @mirtitles@mastodon.social

Bluesky: mirtitles.bsky.social

CONTENTS

Editorial Note vii

O. K. Shcherbakov The Lower Supply System of BESM (the high-speed electronic computer of the Academy of Sciences of the U.S.S.R.) 1

F. V. Maiorov Digital Integrating Machines (Differential Analyzers) 22

P. P. Golovistikov Dynamic Flip-Flops and Their Use in Parallel Action Computers 96

E. A. Voikov A Method of Automatic Monitoring of a Serial Arithmetic Unit 134

L. N. Korolev Methods of Selecting the Required Word from a Dictionary 139

K. Ya. Matyukhin and O. V. Rosnitskii The Role of the Ferrite Core in a Matrix Storage Unit 143

Yu. N. Glukhov and O. V. Rosnitskii Reliability of a Matrix-Type Magnetic Store with Linear Selection 158

E. I. Limonov Basic Nomenclature and Definitions in Automatic Digital Computer Engineering 170

#computerArchitecture #computerSystems #sovietLiterature #sovietTechnology

“Myths Programmers Believe About CPU Caches” [2018], Rajiv Prabhakar (https://software.rajivprab.com/2018/04/29/myths-programmers-believe-about-cpu-caches/).

Via HN: https://news.ycombinator.com/item?id=45767178 & https://news.ycombinator.com/item?id=36333034

#Cache #CacheCoherency #CPU #Hardware #ComputerArchitecture #Intel

Chip Hall of Fame: Intel 8088 Microprocessor

https://spectrum.ieee.org/chip-hall-of-fame-intel-8088-microprocessor

#HackerNews #ChipHallOfFame #Intel8088 #Microprocessor #TechHistory #ComputerArchitecture

x86 architecture 1 byte opcodes

https://www.sandpile.org/x86/opc_1.htm

#HackerNews #x86 #architecture #opcodes #computerarchitecture #programming #technews #assembly

Wanted #ComputerArchitecture pedantry.

What distinction do you guys make between a "cache block" and a "cache line" ?

💡 On EDIC: “I was challenged daily by top peers & great mentorship, building skills I use every day.”

Want to take your research from ideas to real-world innovation?

➡️ Discover the EDIC PhD Program

#EDICPhD #ComputerArchitecture #IntegratedSystems #HardwareSecurity #FutureResearchers #phdchat #academictwitter #WomenInSTEM

Virtual Memory for Real-time RISC-V systems using hPMP

https://arxiv.org/abs/2504.04498

#HackerNews #VirtualMemory #RISC-V #hPMP #RealTime #Systems #ComputerArchitecture

Ah, the ancient art of computer architecture comparison, reduced to a #JavaScript and cookie-enabled abyss 🤦♂️💻. Because who doesn't love waiting for a website to tell us the earth-shattering differences between two processor types that about five people care about? 🍪🔄

https://dl.acm.org/doi/pdf/10.1145/106972.107003 #computerarchitecture #processorcomparison #techhumor #webdevelopment #HackerNews #ngated

Comparing a RISC and a CISC with Similar Hardware Organization

https://dl.acm.org/doi/pdf/10.1145/106972.107003

#HackerNews #RISC #CISC #ComputerArchitecture #HardwareComparison #TechTrends

A Look into Intel Xeon 6's Memory Subsystem

https://chipsandcheese.com/p/a-look-into-intel-xeon-6s-memory

#HackerNews #IntelXeon6 #MemorySubsystem #TechInsights #ComputerArchitecture #ChipsAndCheese

@aka_pugs 🧵100🎂Seymour Cray

‘A Seymour Cray Perspective’

Gordon Bell’s closing quote from Jim Gray

November 10, 1997

@aka_pugs 🧵100🎂Seymour Cray

‘A Seymour Cray Perspective’

Seymour Cray Lecture Series

University of Minnesota

November 10, 1997

Gordon Bell

#seymourcray #computerarchitecture

https://gordonbell.azurewebsites.net/craytalk/sld001.htm

This toot https://fosstodon.org/@interlisp/115122557055111398 led me via a reference to Edmund C. Berkeley (as coauthor with L. Peter Deutsch of "The LISP Implementation for the PDP-1 Computer", March 1964 and author of "Giant Brains, or Machines that Think", 1949) to the 1950 2-bit relay computer Simon and then to Harry Porter's Relay Computer:

https://www.youtube.com/watch?v=tsp2JntuZ3c

By eighteen minutes in, if you can follow along, you'll understand how ALU function codes are selected.

I've never seen such a succinct explanation of a computer.

[Edit: the 3-bit ALU function codes are later wrapped in 8-bit opcodes, which trigger loads and selects from the data and address buses. This is exposition at its finest!]

#computerarchitecture #relaylogic #vintagecomputing #retrocomputing

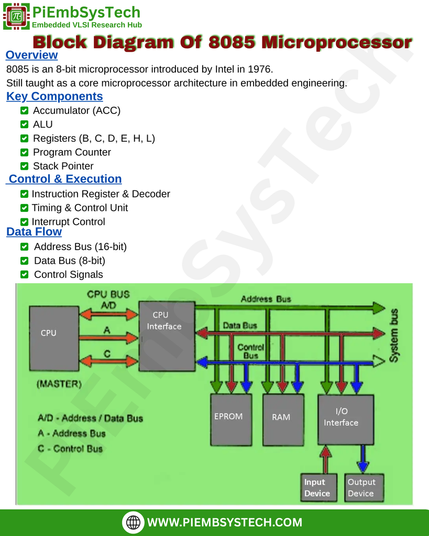

Inside the 8085 Microprocessor – Understanding Its Block Diagram

📱 Learn More with Piembsystech

🔗 Download: https://play.google.com/store/apps/details?id=com.piembsystech&pcampaignid=web_share

🌍 Website: https://piembsystech.com/8085-microprocessor/

#8085Microprocessor #MicroprocessorArchitecture #BlockDiagram #EmbeddedSystems #AutomotiveElectronics #MicroprocessorDesign #ProcessorArchitecture #ECUDevelopment #VehicleElectronics #DigitalElectronics #ComputerArchitecture #EmbeddedDesign #AutomotiveEngineering #MicrocontrollerProgramming #InstructionSetArchitecture

Understand CPU Branch Instructions Better

https://chrisfeilbach.com/2025/07/05/understand-cpu-branch-instructions-better/

#HackerNews #Understand #CPU #Branch #Instructions #Better #CPU #Branching #ComputerArchitecture #TechEducation #CodingInsights