Tomorrow I try the Open source Tool chain for #FPGA first I search #Machxo3 then #ICE40. I am frustrated about the commercial license.

#ICE40

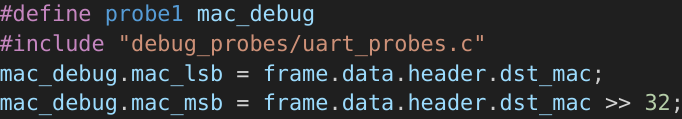

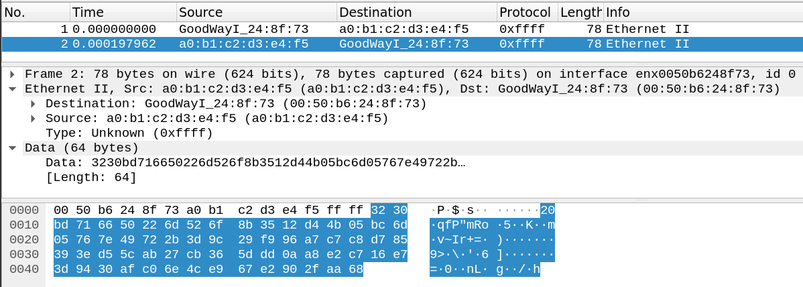

Say I am debugging an #ethernet project on the #ice40 #fpga of pico-ice board. I want to know the contents of some registers down in my design (which destination MAC address my #hardware tried to transmit). I don't want to use manufacturer specific ILAs and don't want to hand route a bunch of debug signals to my top level for external #debug equipment I don't have.

In PipelineC just assign to a globally visible #UART debug probe wire:

https://github.com/JulianKemmerer/PipelineC/wiki/Example:-Debug-Probes

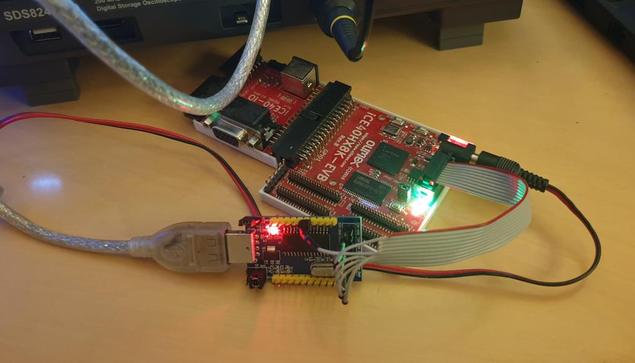

Finally got around to connecting my #olimex #ice40 development board to power again, and getting a bit stream programmed onto it.

(I really haven't played enough with it)

"Back in the day" I'm sure I used a raspberry pi for the programming.

This time I tried using a dirt cheap #ch341a for the programming, its a bit on the slow side, especially when programming all 2MB of SPI flash.

Probably should limit the number of bytes to be programmed and/or switch to one of my #ch347 boards

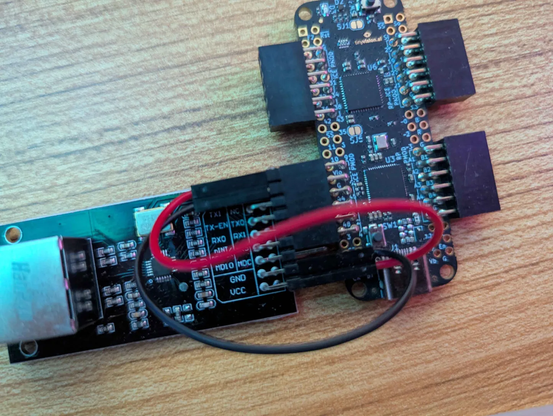

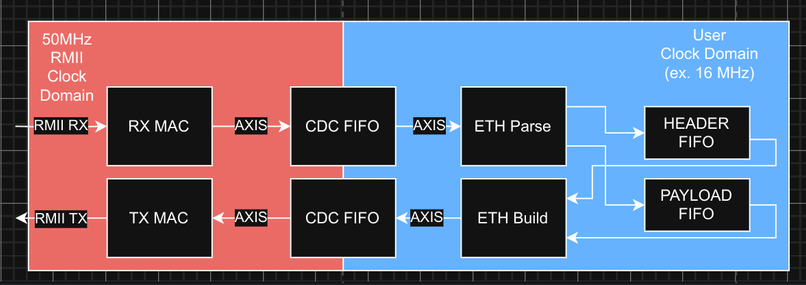

Yay those cheap #hardware #ethernet phy #pmod -LIKE things work with the pico-ice #ice40 #FPGA . Thanks for your help with RMII interface @dutracgi ! #embedded #HDL #RTL #Verilog #VHDL #HLS https://github.com/JulianKemmerer/PipelineC/blob/master/examples/pico-ice/ice_makefile_pipelinec/ethernet_top.c

Learn PipelineC #HDL basics featuring the pico-ice dev board from tinyVision.ai! It has a Lattice Semiconductor @latticesemi #ice40 #FPGA and @Raspberrypi. This intro covers #LED, #UART, and #VGA projects using OSS CAD Suite tools. #hardware #RTL #Verilog #VHDL #HLS

https://www.youtube.com/watch?v=wWdvuAQXeS0

In the mood for the littlest bit of #FPGA #GameDev? 🤓 Check out this pico-ice based #pong demo. Just need #VGA #pmod and #UART connected to host PC. #HDL #hardware #RTL #Verilog #VHDL #HLS #lattice #ice40 https://github.com/JulianKemmerer/PipelineC/blob/master/examples/pico-ice/ice_makefile_pipelinec/pong_top.c

A Curated Directory of Awesome Cologne Chips' GateMate FPGA Links.

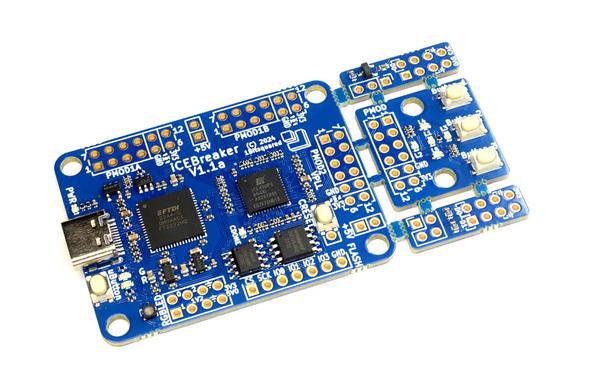

The iCEBreaker FPGA dev board V1.1 is available in the US store right now! Get them while the inventory lasts. The new version features an RGB LED, additional PSRAM chip, USB-C connector, populated “ears”, as well as length matched Pmod signal connections! https://1bitsquared.com/products/icebreaker #opensource #fpga #ice40 #electronics #hacking #openFPGA

Have been super pleased with the #ice40 #FPGA and #raspberrypi board that https://pico-ice.tinyvision.ai/ sent me to experiment with. Many thanks and I look forward to putting together a talk for intro users getting started with #PipelineC and boards like the pico-ice 🤓 #HDL #Verilog #VHDL #hardware #embedded

> Is it possible to program one MicroPython #RP2040 core from the other?

My expertise is on the #ICE40, more than the #RP2040, but reportedly the RP2040 can run two #MicroPython threads on the two cores, so. you should be able to program one from the other.

If not, you can certainly program a #pico-ice #Forth core from the first MicroPython core.

What are you trying to accomplish?

ICE-V Dual and ICE-V Dual Fermatta

These cpus have two cores which share an ALU and control structures. On calls and jumps usually RISC-V computation pauses while the core loads the next instruction and decodes it. By alternating between the two cores, this problem is avoided. And many applications can easily be split into twoth reads sharing the same memory.

By @sylefeb

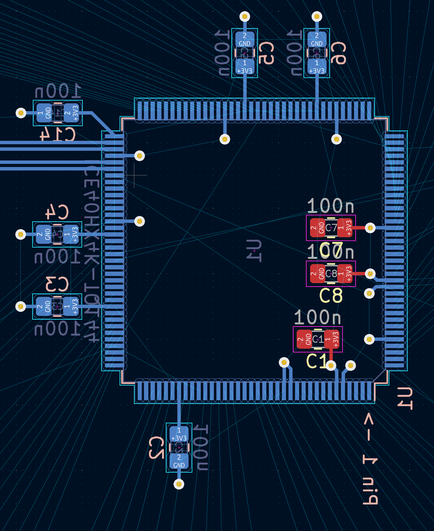

#PBC layout question for anyone who knows more than I do about the subject (essentially everyone)...

Is it ok to put decoupling caps under the #iCE40 package (like the 3 red ones in the image) or am I better off keeping them on the same side as the IC (like the blue ones)? I only have 2 layers to play with and lots of routing on one (still to do on blue), so plan to use the other as (mostly) ground plane and power anyway.

I'm asking before I do the tedious routing ;)

@PaulaMaddox @maxiborga @matthewvenn Also due to the very nice and small #ice40 toolchain

(Yes normal vendor tools I'm looking at you in disgust)

it is quite approachable to getting started with verilog.

And the ice40 family has some very affordable dev kits if you are not satisfied with pure simulation.

A lot of fun can be had with simple projects like writing your own UART.