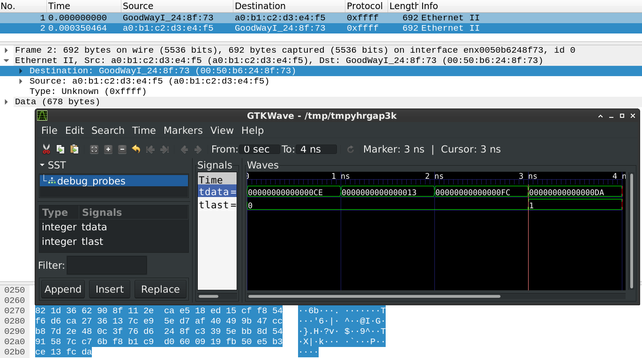

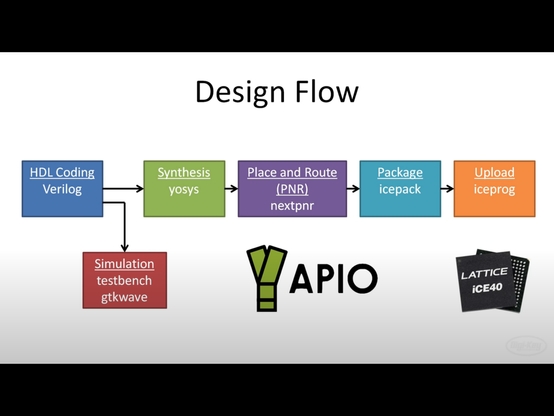

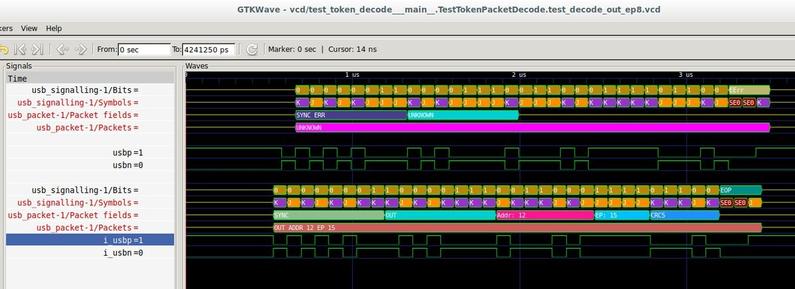

So what can you do with the ability to read arbitrary #FPGA registers out of your design over #UART? Capture time series data (last four #ethernet packet bytes) in your regs and write a little #python script that launches #GTKWave and you have yourself a tiny homemade cross platform logic analyzer thing!

https://github.com/JulianKemmerer/PipelineC/wiki/Example:-Debug-Probes

#gtkwave

Адаптация платы Colorlight 5A-75B для примеров «Школы синтеза цифровых схем»

Привет! Начался новый поток «Школы синтеза цифровых схем» и я хотел бы поделиться своим опытом по адаптации бюджетной платы с ПЛИС для запуска на ней лабораторных работ Школы. Отдельным преимуществом такого решения является возможность использования Open Source маршрута для синтеза и моделирования цифровых схем на базе Yosys и Icarus Verilog. Colorlight 5A-75B не является отладочной платой в привычном понимании этого понятия - будет интересно.

https://habr.com/ru/articles/849592/

#плис #fpga #yosys #lattice #verilog #systemverilog #icarus #gtkwave

@thezoq2 I just tried #surfer for the first time today. Compiled from scratch per the website. I had to file a bug, as it crashes after adding a handful of signals.

I was so hopeful. But for now going back to #gtkwave I'm sad though, because surfer is able to do very simple things like select all the signals at a level and add them to the viewer, whereas gtkwave seems to fight you at every step of the way.

Maybe I need to roll back to a tagged version and rebuild or something. #ghdl #vhdl

Ok so it's still a bit buggy on windows, and ModelSim doesn't play nice.

But combined with #GHDL for open source #VHDL simulation and #gtkwave for wave viewing it's a surprisingly comfortable to set up tool chain, especially on Linux it's all just via package manager and pip~

Now to learn proper file structuring and documenting habits to raise the code quality bar a bit, probably add proper test benches~

Again #TerosHDL helps with built in docs generator <3

If you are using #GTKWave, I recommend adding a .gtkwaverc file to you projects or home dir with the following line

```

do_initial_zoom_fit 1

splash_disable 1

```

The flags do as they say.

You might want to reconsider the first one if you usually deal with huge recordings.

There might be more options that could make your workflow more pleasant.

https://linux.die.net/man/5/gtkwaverc

FPGA Starter Videos To Help Soften That Learning Curve

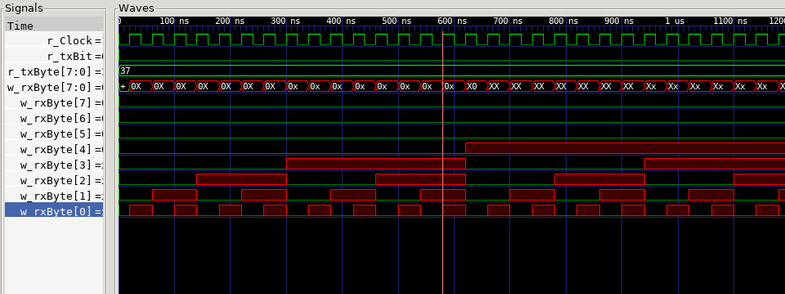

Digi-Key have been producing YouTube videos for a number of years now, and if you weren't aware, they're definitely worthy of some viewing time. The playlist we're highlighting here is a pretty good introduction to FPGAs, specifically those supported by open source tools, with low cost hardware. If you've always wanted to get into hacking FPGA platforms, but don't know where to start, this is going to be a big help. After first covering what an FPGA is and is not, and why you want to use one, [Shawn Hymel] dives in to the toolchain.

We're really lucky that the bitstream for the Lattice iCE40 was reverse engineered by the super talented Claire (née Clifford) Wolf (AMP hour interview) which enabled the project ICEstorm toolchain to be created. Leveraging Yosys for synthesis and logic mapping, Icarus verilog coupled with GTKwave for simulation, netpnr for place and route and finally the project ICEstorm bitstream tools for packing into iCE40 format and loading onto the hardware. The whole toolchain flow is managed by APIO for simplicity, that is, provided your FPGA board is supported!

Of course, [Shawn] is using the low cost (for an FPGA) ICEStick by Lattice for this tutorial series, and they're currently hard to get (you know why by now!) but, there are many other boards you could use. If you want to play with applications coupling a ARM micro to an FPGA, then the excellent BlackIce Mx is an option, but there are many other boards now with an decent micro nestled next to an FPGA and a few peripherals for convenience.

We should mention here, that project ICEstorm and the iCE40 is not the only show in town. Project Trellis has had our eye for a while, which targets the more complex Lattice ECP5 device. Yosys and friends do support more architectures, but the available flows usually require at least some vendor tool support at this time (looking straight at you, Xilinx) but as more devices get decoded, the open source tools will grow, and we will bring you that news!

What's nice about this Digi-Key YT series, is that it doesn't just cover the basic toolchain flow, then drop you in at the deep end of a big learning curve. There are videos covering subjects such as finite state machines (FSMs), test-benching and simulation, using embedded (block) memories, PLLs, harder subjects like dealing with metastability and clock-domain crossing (OK, he covers one technique - there's more than one way to skin that particular cat) before finally looking at soft cores like the RISC-V. Lots to learn, and pretty well executed if you ask us! A Github version is available, for those who can't stand watching the videos!

Thanks to [Mark] for the tip!

#fpga #apio #blackice #gtkwave #icarus #ice40 #icestorm #lattice #mystorm #nextpnr #projecttrellis #yosys

https://lists.riscv.org/g/software/message/174

I would add after 1 or 2 weeks of testing that, Most JIT are missing, not only Lua (there is already a patch for RV32), PCRE, php engine, mb_strings (but they can all be used without it).

Other missing libs: libgsl25 (GNU Scientific Library), needed by Hugin, and Darktable (there is still rawtherapee). #ObsStudio is missing too.

On the sound design part, SuperCollider is missing.

On the (retrocomputer/arcade/console) emulator side missing are: openmsx, but mame, libretro (including bsnes, beetle-psx/vb/pce, desmume, etc...) are here. Missing in libretro are snes9x, and nestopia (closed source)

if Firefox (that already have patchs) and LibreOffice are not in distributions, most productivity tools already have. JHere is a partial list of what is already running on RISC-V:

* GFX: #GIMP, #Krita, #Blender, #Inkscape, #MyPaint,, #Pencil2D, #Glaxnimate, #SynfigSudio, #zopfli, #Imagemagick, #Scribus, #FontForge, #FontMatrix, #Xsane, #LaTeX, #svtAV1 (#av1)

* Audio: #LMMS, #Ardour, #MuseScore, #Fluidsynth, #VMPK, #zynaddsubfx #pipewire #sox, #Audacity, #TuxGuitar, #CheeseCutter, #SfxrQt, #BambooTracker (YM2608/OPNA), #GoatTracker (C64), #HivelyTracker (AHX, HVL), #MilkyTracker

* Photo/Video: #mpv, #pipwire, #mencoder, #ffmpeg, #shotcut, #kdenlive, #pitivi, #vlc, #mlt, #melt, #vokoscreenNG, #RecordMyDesktop, #entangle, #rawtherapee, #guvcview, #UVCcapture, #Cheese

* OS: #qemu, #uae, #DosBox

* Dev: #GCC, #LLVM, #FPGAtools, Geany, #YoSys, #QtCreator, #Fritzing, #WireShark, #GTKWave, #Verilator

* Web services: #nginx, #apache, #php, #python, #lua, #ruby

* Internet clients: #hexchat, #WeeChat, #Gajim, #Xmppc, #TelegramDesktop, #Epihany, #netsurf, #Filezilla,

* Game engines: #tic80, #LÖVE, #PyGame, #Cube2, #Scummvm, #LibRetro

* Map: #Marble, #Stellarium (stars map)

* Games (not depending on a game engine): #SuperTuxKart, #ExtremeTuxRacer, #NeverBall, #bzflag, #Wesnoth...

* SImulation: #FlightGear,